ggoggo

5.5 반도체 메모리 본문

1. 반도체 메모리 용어

- 메모리 셀(cell) : 디지털 정보의 최소 단위인 1비트를 저장하는 소자

- 메모리 워드(word) : 1,2,4,8,16,32,64,128비트로 커지며 칩의 설계마다 다름

- 저장용량(capacity)

- 저장 매체에 저장된 정보비트의 수량

개별 메모리 칩은 대개 비트 단위로 표시

메인 메모리용 램 모듈은 주로 바이트 단위로 표시

- 칩이나 램 모듈의 저장 구소(organization)

저장 주소의 개수와 메모리 워드의 비트수를 곱해 저장밀도[ (주소 수) x (비트 수) ] 표시

ex. 메모리 칩 구조 256M x 4 => 256M개의 저장주소, 4( = 2^2)비트의 메모리 워드를 갖는 1Gib 용량

- 메모리 뱅크(bank)

- 기억장치를 분할해 독립적으로 액세스할 수 있도록 구성한 논리적인 단위, 한번에 하나의 뱅크만 액세스

- 뱅크의 크기는 논리적이라 구성하기 나름

- 전형적인 DRAM 칩에서 뱅크

- 여러개의 행과 열로 구성된 격자구조의 저장단위

- 랩 모듈은 이런 구조가 여러 개의 칩에 걸쳐 연결

- 메모리 칩 내부의 저장 위치 구조

- (뱅크 수) x (행 수) x (열 수) => 저장 주소의 총 개수

- 뱅크 내부는 (행수) x( 열수)의 메모리 격자 구조

- 메인 보드의 램 모듈도 뱅크로 구분할 수 있음

- 메모리 컨트롤러와 이를 장착할 메모리 슬롯의 물리적인 구조에 의해 결정

2. ROM과 RAM

ROM(read only memory)

- 읽기 전용 메모리

- 보통의 방법으로는 읽을 수만 있는 메모리

- 전원이 없어도 내용이 재워지지 않는 비휘발성 메모리의 일종

- 내용이 쉽게 변경되지 않아야 할 프로그램들 저장

ex. 시스템 시동과 관련된 초기화 프로그램, 진단 프로그램, 시스템에서 자주 호출하는 서브루틴, CPU 내부 제어장치의 마이크로프로그램 등

- ROM 과 반대되는 용어 : RWM(read write memory) => 반대용어로는 보통 RAM 사용

RAM(Random access memory)

- 일반적으로 RAM은 데이터 보존을 위해 전원이 필요한 휘발성 메모리를 통칭하는 말

- NVRAM(non-volatile RAM) : 데이터를 보존하는데 전원이 필요 없고 읽고 쓰기도 가능한 메모리

- 찾는 주소에 따라 액세스 타임이 일정한 메모리

- 반도체 메모리와 자기디스크 등 대부분의 기억장치

- RAM과 반대되는 SAM(sequential access memery)

- 반도체 ROM의 종류

1) 마스크 롬(mask ROM) : 반도체 공정에서 마스크 필름(mask film)으로 인쇄하듯 대량생산하는 롬

2) PROM (programmable ROM) : 퓨즈(fuse)를 녹이면 끊어지는 구조로 한번 프로그램 하면 지울 수 없음

3) EPROM(erasable PROM)

- 지우고 다시 쓰는 것이 가능

- 지울 떄는 상단의 투명한 유리창을 통해 자외선으로 데이터를 일괄 소거, 기록할 떄는 디지털에서 일반적으로 사용하는 전원보다 높은 12V 등 사용

4) EEPROM(electrically EPROM) : 디지털회로에서 일반적으로 사용하는 5V이하의 낮은 전압으로 쓰고 지울 수 있음

- 플래시 메모리(flash memory)

- 대중적인 비휘발성 램(NVRAM), EEPROM의 한 형태지만 과거 전통방식과 구분되는 장점

=> EEPROM과 달리 큰 블록 크기들을 사용할 수 있어 지우는 속도가 빠르고 일괄 소거 가능, 특히 가격 저렴!

- 메모리 카드가 들어가는 디지털 카메라, 휴대전화 등 각종 휴대용 기긱와 USB 드라이브 등에 널리 쓰임

=> 아직 가격이 문제이나 이동용 컴퓨터부터 물리적으로 취약하고 부피가 큰 HDD를 빠르게 대체

- 기존 디지털 기기의 설정 값을 저장하는 용도로 쓰이던 EEPROM과 배터리 백업 받던 SRAM을 대체

- 플로팅게이트(floating gate)의 충전과 방전을 이용하여 1소자 당 1비트인 간단한 구성

=> DRAM보다 단위셀 면적이 작아 대용량에 유리하고 소비전력도 작고 저렴하나, 쓰기 속도 느림,,,ㅜ

=> 메모리 내부 셀이 NAND와 NOR논리 게이트와 유사

1) NAND 타입

-> 몇 개의 블록 단위로 읽고 쓸 수 있음

-> 대용량이 요규되는 메모리 카드, USB 드라이브 등

2) NOR 타입

-> 대개 바이트인 메모리 워드 단위로 읽고 쓸 수 있음

-> 과거 EPROM을 대체하여 빠른 속도가 요규되는 기계어 코드 수준이 응용설계에 주로 사용

* 비트(0,1) < 바이트(=8비트) < 워드(컴퓨터 설계 시 정해지는 메모리의 기본단위)

- SRAM과 DRAM

1) SRAM (static Ram)

- 교차결합 인버터의 스위칭을 이용하는 쌍안정 회로

- 트랜지스터 6개 정도로 1비트 저장하는 안정된(static) 저장구조, 전원만 공급받으면 리프레시 회로 필요없음

- DRAM보다 비싸지만 액세스 타임이 빠름

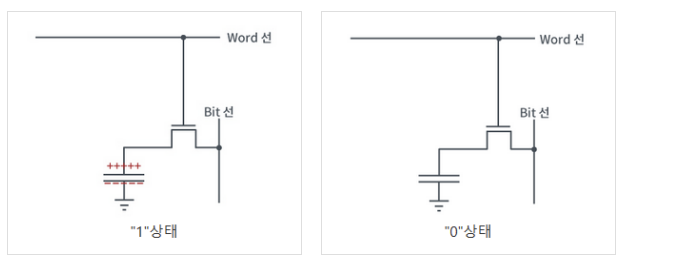

2) DRAM (Dynamic ram)

- 커패시터의 충전과 방전을 이용해 최소 트랜지스터 1개와 커패시터로 1비트를 저장하는 간단한 구조

- SRAM보다 가격이 저렴하고 대용량 설계가 용이하나 전하의 충전상태가 안정적이지 못하고 동적(dynamic)

- 셀 안의 저장 상태가 유지되도록 주기적으로 충전 전압을 올려주는 리프레시(refresh)회로 필요

- 사이클 타임(cycle time)

- 메모리 용어에서 기억장치에서 연이은 액세스를 새로 시작하는데 걸리는 시간 간격

- SRAM => 사이클 타임 = 액세스 타임

- DRAM => 사이클 타임 = 액세스 타임 * 2

-> 리프레시 진행되는 동안 새로운 액세스를 시작할 수 없어 연속 액세스하려면 액세스 타임의 약 2배 필요

3. DRAM 구조

- RAS(행 주소를 지정)와 CAS(열 주소를 지정) 신호를 주소 선과 함께 보내 각 저장 위치의 주소를 완성

ex. 512M x 8 4Gb 칩 내부 <8뱅크 x 16행 x 10열>

- 3개의 뱅크 선택선

- 16개의 메모리 주소 선

- 뱅크 내부 => 행주소 A15 ~ A0, 열주소 A9~A0사용

=> 총 저장주소 수 = 2^3 x 2^16 x x 2^10 = 2^29 => 512M

- 8개의 데이터 버스 선

- 칩의 (저장밀도) = (주소 수) x (비트 수) = 512M x 8 = 4Gib

- DRAM 리프레시

RAS가 가해진 모든 행에 걸린 셀의 내용이 한 번에 재충전되는 방식 등을 사용

- 재충전 시간 때문에 DRAM을 연속 액세스하려면 => 액세스 타임의 2배 정도 필요!

- 특정 셀의 내용을 읽어오면 출력으로 전압이 떨어져 강제로 재충전 해주어야 하고,

- 특정 셀에 쓰면 그 행에 걸린 모든 열의 셀이 재충전되므로 기다려야함

4. 램 모듈

램모듈(RAM module)

주로 컴퓨터의 메인 메모리로 사용하기 위해 시스템 보드에 장착하기 적합하도록 만들어진 부품

-> 대개 DRAM 칩을 결합한 보드 형태로 메인보드에 장착

- 메모리 랭크(rank)

- 공통의 버스에 연결되어 동시에 동작하는 칩들의 모임

- 주로 같은 칩 선택 신호에 연결되어 동시에 액세스가 가능한 DRAM 칩들의 집합

- 메모리 칩들은 모두 같은 메모리 주소버스와 데이터버스에 연결되지만 물리적으로 여러 랭크로 나눔

- 램 모듈의 데이터버스 비트 수

=> 칩 당 메모리 워드의 비트수와 랭크 당 칩의 개수를 곱한 것

DDR 램 모듈은 보통 64비트

에러 정정 코드(error-correcting code)를 갖는 ECC 램 모듈은 에러 정정 8비트 추가해 보통 72비트

- 메인 보드가 결정되면 램 모듈이 결정

- CPU와 메모리 컨트롤러에 따라 램 모듈 방식이 결정(권장 종류 따라야함)

- 허용되는 시스템 버스의 클럭 속도가 빠를수록 고성능

- 램 모듈의 저장구조

- 칩의 구조처럼 저장 주소의 개수와 데이터버스의 비트수를 곱함 => (주소 수) x (비트 수)

- 1G x 64 표시 램 모듈 => 1G개 저장 주소와 64비트 데이터버스로 구성된 8Gib 용량의 램 모듈

- 램 모듈의 구성

- 칩의 저장 구조에 칩의 수를 곱해 => (주소 수) x (비트 수) x (칩의 개수)로 표시

- 512M x 8*16pcs로 표시된 64비트 램 모듈이 구성

=> 512M x 8 구조의 8비트 4Gib 칩 16개(pieces)

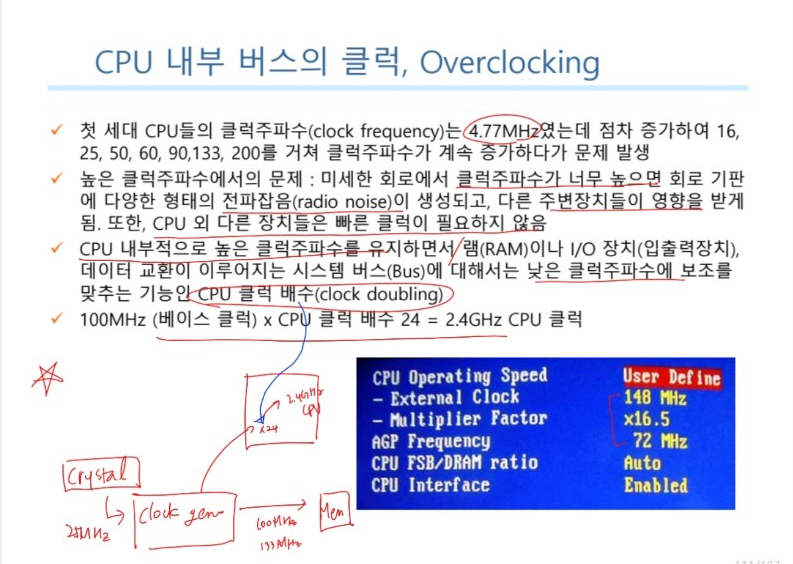

- Clock generator

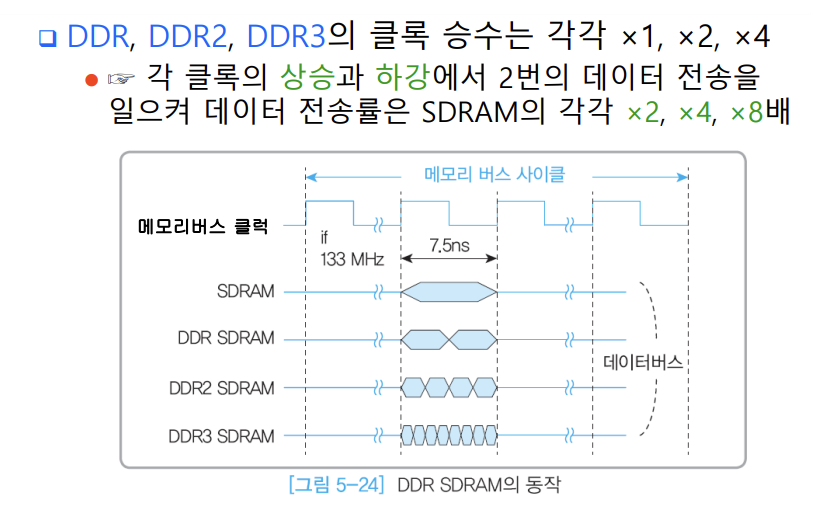

5. DDR SDRAM

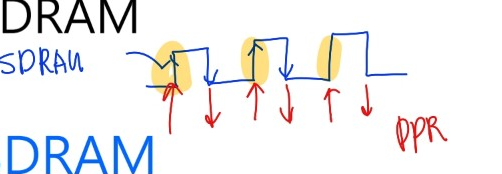

SDRAM(synchronous DRAM)

: 메모리 컨트롤러가 아닌 메모리 버스 클럭에 직접 동기(synchronous)되는 DRAM

DDR(double data rate) SDRAM

: 같은 메모리 클럭 속도에서 SDRAM에 비해 "2배의 데이터 전송률"을 갖는 DRAM

- 클럭 펄스의 상승, 하강 시점에서 각각 한번의 데이터 전송

- 클럭 속도가 물리적으로 증가하는 것은 아니지만 버스 사이클 하나 당 전송횟수를 늘려 대역폭을 증가

반도체 칩의 클럭 승수(clock multiplier)

: 반도체 칩 내부의 동작 클럭이 외부 공급 클럭의 몇 배수인가를 표시 xn

=> DDR2, DDR3, DDR4ㅡ이 클럭 승수는 각각 x2,x4,x8

=> sdram에 비해 데이터 전송률 x4, x8, x16

선인출(prefetch)

: 작업이 빨리 실행되도록 필요한 자료를 미리 읽어들이는 기능

DDR 방식은 선인출 버퍼에 여러 비트를 미리 준비해 한 메모리 버스 사이클 당 여러번의 데이터 전송

- 메모리 버스의 클럭

- 메모리, CPU, 메모리 컨트롤러는 그 이상도 지원하나 칩 내부의 성능일 뿐 메인보드가 병목현상

- 칩을 표시 클럭보다 낮게 사용하는 것은 문제 없음

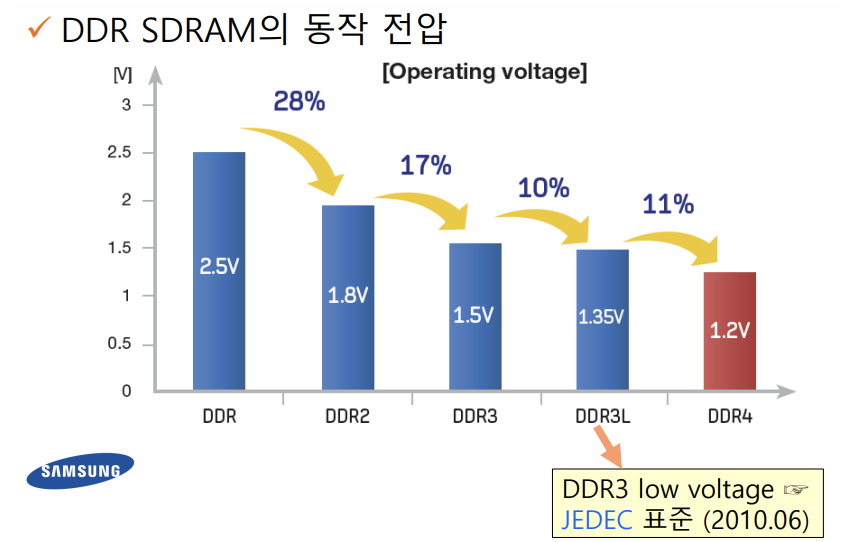

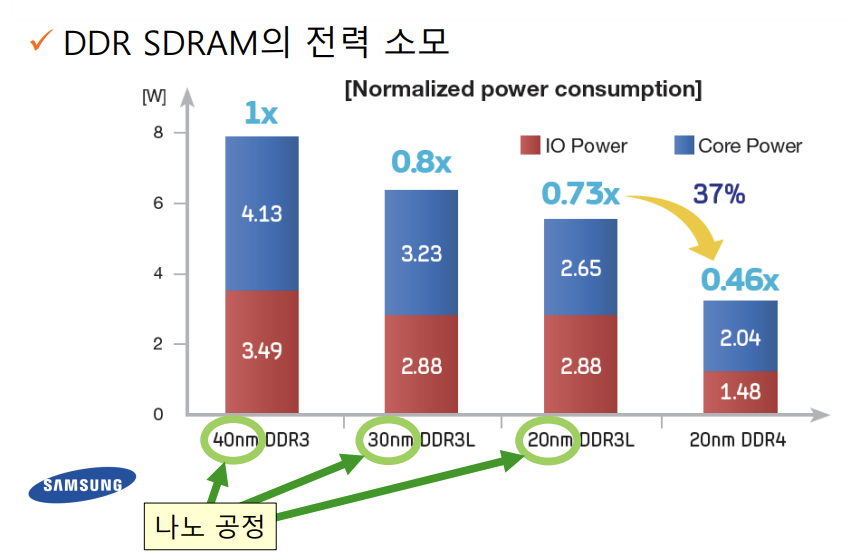

6. 클럭 속도와 전압

- 클럭 속도를 높이려면 동작 전압을 낮춰야함! -> 발열 down

- 액세스 횟수가 빈번해지거나 동작 클럭이 빨라지면 => 소비전력 증가 => 발열 증가

- 발열 줄이려면 전력 소모 줄이기 위해 동작 전압 줄이기(0,1 구분하는 전압 차) -> 클럭 속도 높임, 발열 down

- 반도체 나노 공정 기술로 가능

=> 고밀도 반도체 설계기술로 좁은 회로선 폭과 짧은 배선 거리 구현

=> 회로의 집적도 증가 => 전기 신호의 이동거리 감소 => 낮은 전압 사용이 가능 => 전력 소모 감소 => 발열 감소

'3-1 > 컴퓨터구조 및 운영체제' 카테고리의 다른 글

| 5.6 시스템 버스의 대역폭 (0) | 2022.06.15 |

|---|---|

| 운영체제 : Ch3. Processes (0) | 2022.06.15 |

| 운영체제 : Ch2. Operating-System Services (0) | 2022.06.15 |

| 운영체제 : Ch 1.1 Operation System (0) | 2022.06.11 |

| 운영체제 : Ch 1.3 Storage Management (0) | 2022.06.10 |