ggoggo

5.3 캐시메모리 본문

- 캐시메모리(cache memory, cpu cache)

- 주로 메인메모리의 액세스타임을 줄이기 위해 사용하는 메인메모리와 cpu 사이에 사용하는 빠른 속도의 메모리

- 프로그램이 사용 중인 근방을 저장

(자주 액세스하는 데이터나 프로그램 명령을 반복해 검색하지 않고 즉시 사용할 수 있도록 준비)

- 주로 액세스 타임이 빠른 SRAM 사용

- CPU에 아주 가까이 혹은 내장

1. 캐시와 메모리 계층

- 캐시로 메모리 계층 간 속도 차이를 완충시켜 전체 기억장치의 평균 액세스 타임을 줄임

- L3, L2, L1으로 올라갈수록 속도는 증가, 크기 축소

- cpu는 상위계층부터 자료를 찾아 없으면 차례대로 하위계층으로 내려가면서 찾음

(L1 -> L2 -> L3 -> 메인메모리 -> 하드디스크, 하위계층에 대한 액세스가 늘어날수록 평균속도가 느려져 전체 기억장치의 성능 저하)

- 캐시 성능 개선방법

1) 캐시의 위치 : CPU 코어 내부 > CPU 언코어 > CPU 칩 외부

2) 같은 CPU 코어 일때 -> CPU코어 클럭 증가, 내장 캐시의 성능개선(용량&연결 속도 개선), 멀티코어 구조

3) 내장 캐시의 연결 속도 개선 -> 비트 수와 클럭 증가

- L1, L2, L3 캐시

- L1 캐시 : 명령 캐시와 데이터 캐시 분리

슈퍼스칼라 방식으로 병렬처리를 설계하기 유리

→ L1 데이터 캐시 : 동시에 읽고 쓰기 가능하도록 데이터 출입구를 두개로 분리한 듀얼포트 SRAM 사용

- L2, L3 캐시 : 명령과 데이터가 공유

→ L2 캐시는 프로세서 칩 내부의 다른 공유 장치들과의 버스 인터페이스 속도를 높이기 위해 사용

→ L3 캐시는 멀티코어 간의 다중작업이나 하나의 작업을 나눠서 처리할 때 일관성 유지

- 온-다이 캐시

- 온 다이(on-die) : 캐시가 CPU 코어와 같은 반도체 회로기판 위에 있다는 뜻

- 온 칩(on-chip) : 같은 칩 안에 있다는 뜻

** 멀티코어 프로세서에서 코어(core), 언코어(uncore)의 개념**

- 코어(core) : 독립적으로 명령을 실행하는데 필요한 부분

ex) ALU, 레지스터, 부동소수점 처리장치(FPU), 독립적인 명령어 실행장치, 단독으로 사용하는 L1, L2 캐시 등

- 언코어(uncore) : 내장된 장치 중 코어가 아닌 부분

각 코어가 공통으로 공유해 사용할 수 있는 부분

ex) 명령어 인출과 해동장치, L3 공유 캐시와 칩 내부에 내장된 메모리 컨트롤러, 버스 컨트롤러, 그래픽 처리장치(GPU) 등은 코어 개념에서 제외

- 디스크 캐시

- 디스크 캐시(disk cache)

: HDD, ODD 등 디스크의 액세스 타임을 줄이기 위해 CPU와 디스크 장치 사이에 사용하는 캐시메모리

+) 디스크에서 데이터를 읽고 쓰는 법 : 디스크 컨트롤러와 I/O버스 컨트롤러 거침. 이들 장치에 분산된 버퍼도 중간 단계에서 일종의 디스크 캐시 역할 함

운영체제에 의해 주로 메인메모리의 일부를 할당됨

→ 메인메모리의 상당 부분을 할당(많게는 1/3)

→ 디트스 캐시를 늘리면 메인메모리가 줄어 가상메모리를 늘려야 하므로 적절한 비율을 OS가 자동 관리

cf. 하드디스크에 내장된 디스크 버퍼(disk buffer) → HDD를 읽고 쓸 때 임시로 저장해두는 버퍼 메모리

2. 전면버스와 후면버스

- 메모리의 이중독립버스(dual independent bus)

메모리 버스가 두 개의 독립적인 버스를 갖는 구조

1) 외부 시스템 버스 : CPU와 메인메모리 사이

2) 내부 캐시 버스 : CPU 코어와 캐시 사이

- 전면버스(front-side bus, FSB)

- 주로 CPU와 외부 메인메모리를 연결하는 시스템 버스

- 램 모듈 속도나 시스템 버스의 클럭등을 언급할 때

- 후면버스(back-side bus, BSB)

- 주로 CPU 내부에 내장된 캐시와 CPU 코어 사이를 연결해주는 캐시 버스

- FSB보다 비트 수를 넓히고 클럭도 고속으로 설계

3. 캐시 적중과 실패

CPU가 액세스한 내용은 일단 캐시에 복사됨.

→ 캐시 데이터는 CPU가 요구할 때 신속히 재사용됨

→ 캐시 용량 한계 존재해 한동안 사용되지 않았던 내용은 빠져나감

- 캐시 적중(hit)

CPU가 원하는 내용을 캐시에서 발견한 상태

→ 캐시에서 CPU로 정보 읽어옴

- 캐시 실패(miss)

CPU가 원하는 내용이 캐시에 없는 상태

→ 메인 메모리나 그 아래 곛으에서 읽어옴

- 캐시 적중률(hit rate)

H = (캐시 적중 회수) / (전체 메모리 액세스 회수) x 100

- 캐시가 커지면 적중률이 높아짐

→ 적중률이 높을수록 전체 기억장치의 평균 액세스 타임이 빨라져 캐시의 액세스 타임에 가까워짐

- 캐시 실패율(miss rate) : 1 - H

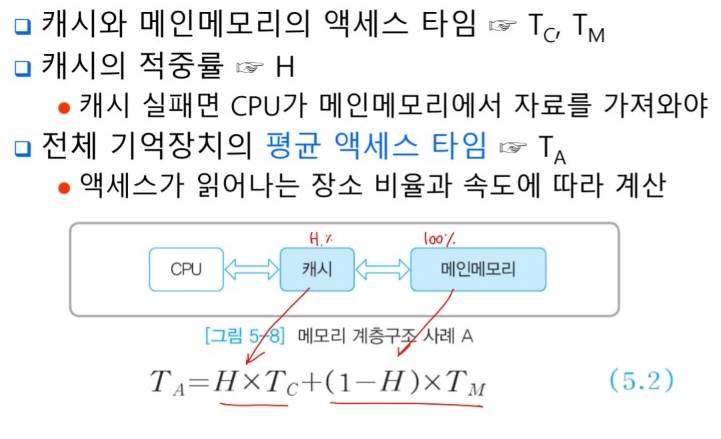

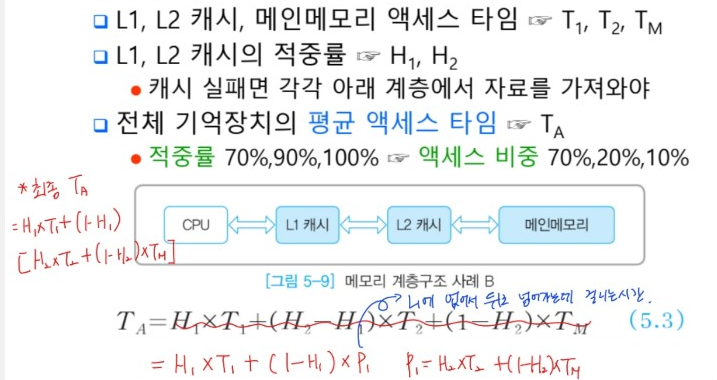

4. 평균 액세스 타임

- 캐시가 적용된 메모리 계층구조 사례 1

- 캐시가 적용된 메모리 계층구조 사례 2

5. 지역성과 일관성

캐시의 목적 = 전체 기억장치의 평균 액세스타임을 줄이는 것

→ 상위계층에 데이터가 존재할 확률을 높여야함

- 캐시 설계 시 고려사항

1) 액세스 타임이 빠른 소자 : 캐시와 메인메모리

2) 데이터의 지역성 : 블록 단위로 현재 필요한 정보와 앞으로 예측되는 정보를 함계 인출

3) 캐시와 메인메모리의 데이터의 일관성 : 캐시의 내용을 변경할 때 메인 메모리의 내용을 함께 바꾸어 주어야 함. (이때 걸리는 시간을 최소화 해야함)

4) CPU 발열문제 : 적중률 ↑ 시, 소비전력↑ 발열량↑

- 데이터의 지역성

- 컴퓨터 시스템에서 지역성(locality)

→CPU가 기억장치의 특정 부분에 위치한 프로그램이나 데이터를 빈번히, 집중적으로 액세스하는 현상

→데이터의 분산 정도를 나타냄

→ 캐시 적중률에 가장 큰 영향

ex) 지역성 좋다 = 현재 사용중인 프로그램들은 CPU에 가까운 메모리 상위계층에 집중

지역성 나쁘다 = 데이터가 여러계층에 분산

1) 시간적 지역성

CPU에서 한번 참조한 프로그램이나 데이터는 조만간 다시 참조될 가능성이 높음.

2) 공간적 지역성

한번 참조된 데이터 주변에 인접한 데이터는 같이 침조된 가능성이 높음 → 인접 저장된 배열 데이터

대부분의 프로그램 명령어는 분기가 발생하기 전까지 기억장치에 저장된 순서대로 실행됨 → 순차적 지역성

- 데이터의 일관성

- 메인 메모리와 캐시 간 데이터의 일관성

메인메모리(CPU가 본래 액세스하려한 위치)와 복사본인 캐시는 데이터의 일관성이 유지 관리되고, 이때 걸리는 시간도 최소화해야함.

캐시가 갱신될 때 메인메모리도 함께 갱신되어야 둘 사이의 매핑구조가 정상적으로 유지

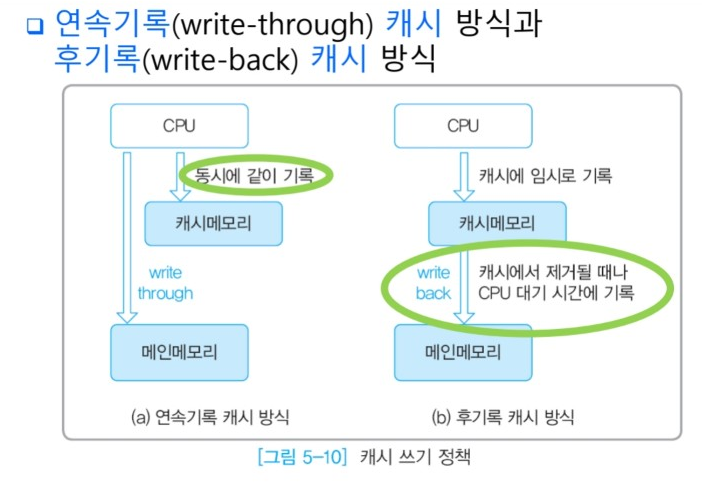

6. 쓰기 정책

- 캐시 쓰기 정책(wirte policy)

캐시의 블록이 변경되었을 때 메인메모리의 블록을 갱신하는 방법과 시기를 정하는 것

- 연속기록(write-through) 캐시

CPU가 캐시와 메인메모리 두 군데 데이터를 정상적으로 함께 갱신하는 방식

속도가 빠른 캐시가 먼저 업데이트된 후 느린 메인메모리에 기록이 완료

→ 구조는 간단하지만 캐시가 갱신될 때, 느린 메인메모리를 매번 함께 액세스하므로 성능 저하

→ 가상메모리에 적용하면 시간이 더욱 오래 걸림

- 후기록(write-back) 캐시

CPU가 캐시의 데이터만 우선 변경하고 메인메모리는 나중에 갱신하는 방식

평상시 : 캐시의 냉요을 메인메모리에 매번 백업하지 않고 변경된 자료를 표시만 하고 캐시를 계속 사용하고 나중에 그 자료가 교체될 때 메인메모리에 없는 내용이면 메인메모리로 복사한 후 자료를 캐시에서 비워줌.

CPU 기계 사이클이 대기 상태로 여유가 있을 때 캐시의 내용을 메인메모리에 블록단위로 수시로 미리 백업해두면 시스템 성능을 더 높일 수 있음.

- 캐시 읽기

연속기록 캐시이든 후기록 캐시이든 걸리는 시간 동일

캐시 적중일 경우 CPU가 캐시에서 , 실패이면 메인메모리에서 원하는 데이터를 읽어옴

- 캐시 쓰기

캐시의 내용이 변경되는 경우에 발생

1) 연속기록의 쓰기 동작 : 항상 함께 기록하므로 느린 메인메모리의 액세스 타임만큼 걸림

2) 후기록의 쓰기 동작 : 캐시 적중이면 캐시를 액세스하고 실패면 메인메모리를 액세스 하므로 읽기 동작과 같아짐.

-> 캐시를 다 채운 후 캐시적중에 실패하면 자료가 교체되어 메인메모리로 옯겨져 기록됨

7. 교체 정책

- 캐시 알고리즘 or 교체 정책

캐시 적중에 실패할 경우, 캐시의 내용 중 교체되어 나갈 자료를 결정하는 것

가장 이상적인 목표는 미래에 가장 오랫동안 필요로 하지 않는 자료를 교체하는 것!

<캐시 알고리즘>

(1) 선입선출(FIFO) : 가장 먼저 들어온 자료를 먼저 교체

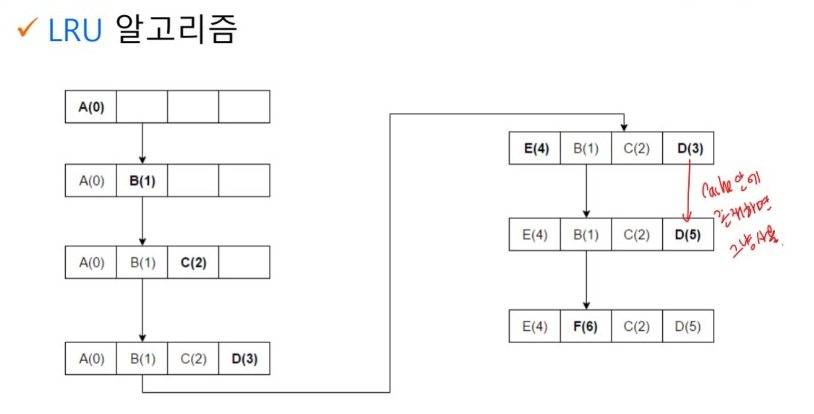

(2) 가장 오래전 사용(LRU) : 가장 오래 전 사용된 자료를 먼저 교체

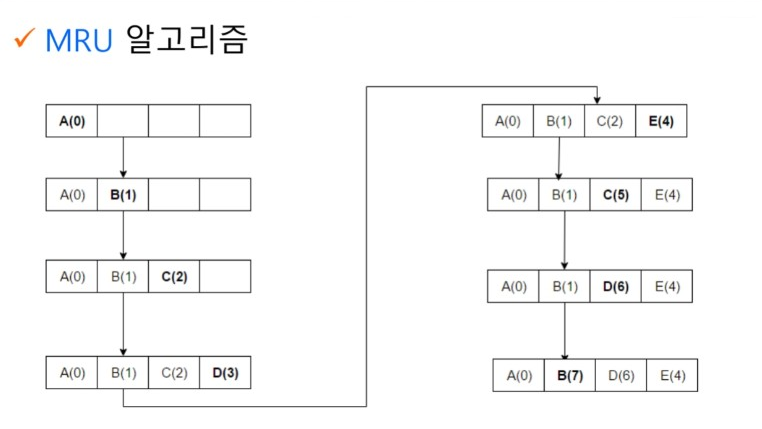

(3) 가장 최근에 사용(MRU) : 가장 최근에 사용된 자료를 먼저 교체

(4) 최소 빈도 사용(LFU) : 사용 횟수가 가장 적은 자료를 먼저 교체

- MRU 알고리즘

- LRU 알고리즘

'3-1 > 컴퓨터구조 및 운영체제' 카테고리의 다른 글

| 운영체제 : Ch 1.3 Storage Management (0) | 2022.06.10 |

|---|---|

| 운영체제 : Ch 1.2 Overview of Computer System Structure (0) | 2022.06.10 |

| 5.4 캐시 매핑 방식 (0) | 2022.05.29 |

| 5.2 메모리 계층구조 (0) | 2022.05.12 |

| 5.1 기억장치 (0) | 2022.05.11 |